16-laag PCB's bied die kompleksiteit en buigsaamheid wat deur moderne elektroniese toestelle vereis word. Bekwame ontwerp en keuse van stapelreekse en tussenlaagverbindingsmetodes is van kritieke belang om optimale bordprestasie te bereik. In hierdie artikel sal ons oorwegings, riglyne en beste praktyke ondersoek om ontwerpers en ingenieurs te help om doeltreffende en betroubare 16-laag stroombaanborde te skep.

1. Verstaan die basiese beginsels van 16-laag PCB's stapelvolgorde

1.1 Definisie en doel van stapelvolgorde

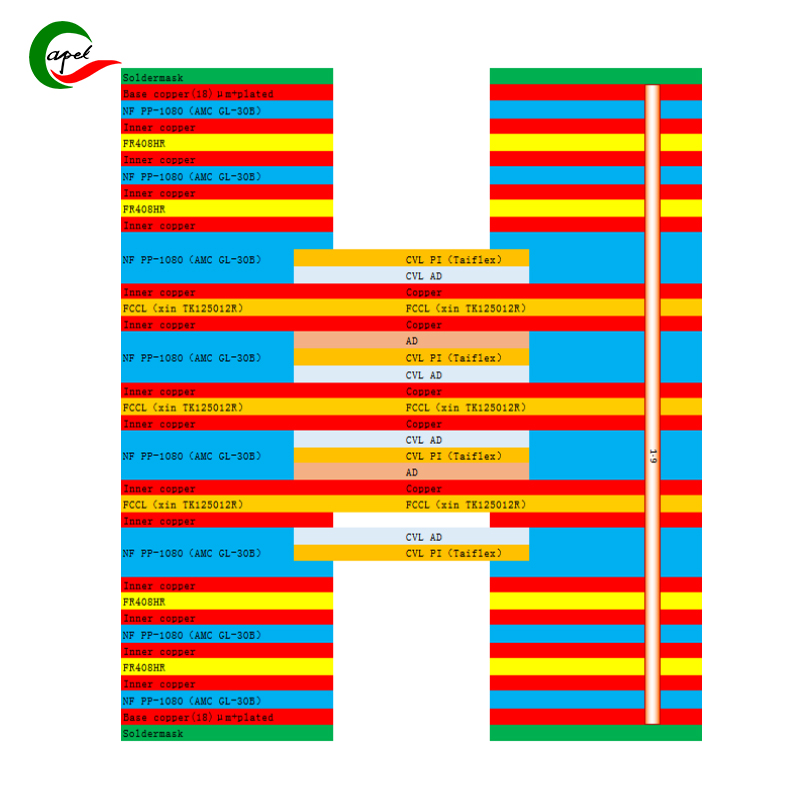

Stapelvolgorde verwys na die rangskikking en volgorde waarin materiale soos koper en isolerende lae saam gelamineer word om 'n meerlaagse stroombaanbord te vorm. Die stapelvolgorde bepaal die plasing van seinlae, kraglae, grondlae en ander belangrike komponente in die stapel.

Die hoofdoel van die stapelvolgorde is om die vereiste elektriese en meganiese eienskappe van die bord te bereik. Dit speel 'n belangrike rol in die bepaling van 'n stroombaanbord se impedansie, seinintegriteit, kragverspreiding, termiese bestuur en vervaardigingsuitvoerbaarheid. Die stapelvolgorde beïnvloed ook die algehele werkverrigting, betroubaarheid en vervaardigbaarheid van die bord.

1.2 Faktore wat stapelvolgorde-ontwerp beïnvloed:Daar is verskeie faktore om in ag te neem wanneer die stapelvolgorde van 'n

16-laag PCB:

a) Elektriese oorwegings:Die uitleg van sein-, krag- en grondvlakke moet geoptimaliseer word om behoorlike seinintegriteit, impedansiebeheer en vermindering van elektromagnetiese interferensie te verseker.

b) Termiese oorwegings:Die plasing van krag- en grondvlakke en die insluiting van termiese vias help om hitte doeltreffend te verdryf en die optimale bedryfstemperatuur van die komponent te handhaaf.

c) Vervaardigingsbeperkings:Die stapelvolgorde wat gekies word, moet die vermoëns en beperkings van die PCB-vervaardigingsproses in ag neem, soos materiaal beskikbaarheid, aantal lae, boor-aspekverhouding,en belyning akkuraatheid.

d) Koste-optimering:Die keuse van materiale, aantal lae en opstapel-kompleksiteit moet ooreenstem met die projekbegroting, terwyl die vereiste werkverrigting en betroubaarheid verseker word.

1.3 Algemene tipes 16-laag stroombaan stapelreekse: Daar is verskeie algemene stapelreekse vir 16-laag reekse

PCB, afhangende van die verlangde werkverrigting en vereistes. Enkele algemene voorbeelde sluit in:

a) Simmetriese stapelvolgorde:Hierdie volgorde behels die plasing van seinlae simmetries tussen krag- en grondlae om goeie seinintegriteit, minimale oorspraak en gebalanseerde hitte-afvoer te verkry.

b) Opeenvolgende stapelvolgorde:In hierdie volgorde is die seinlae opeenvolgend tussen die krag- en grondlae. Dit bied groter beheer oor laagrangskikking en is voordelig om aan spesifieke seinintegriteitvereistes te voldoen.

c) Gemengde stapelvolgorde:Dit behels 'n kombinasie van simmetriese en opeenvolgende stapelorders. Dit laat aanpassing en optimalisering van die opstelling vir spesifieke dele van die bord toe.

d) Sein-sensitiewe stapelvolgorde:Hierdie volgorde plaas sensitiewe seinlae nader aan die grondvlak vir beter geraasimmuniteit en isolasie.

2. Sleuteloorwegings vir seleksie van 16-laag PCB-stapelvolgorde:

2.1 Seinintegriteit en kragintegriteit-oorwegings:

Die stapelvolgorde het 'n beduidende impak op die seinintegriteit en kragintegriteit van die bord. Behoorlike plasing van sein- en krag-/grondvlakke is van kritieke belang om die risiko van seinvervorming, geraas en elektromagnetiese interferensie te verminder. Sleuteloorwegings sluit in:

a) Seinlaagplasing:Hoëspoed seinlae moet naby die grondvlak geplaas word om 'n lae-induktansie-terugpad te verskaf en geraaskoppeling te minimaliseer. Seinlae moet ook versigtig uitgelê word om seinskeef en lengtepassing te minimaliseer.

b) Kragvlakverspreiding:Die stapelvolgorde moet voldoende kragvlakverspreiding verseker om kragintegriteit te ondersteun. Voldoende krag- en grondvlakke moet strategies geplaas word om spanningsval, impedansiediskontinuïteite en geraaskoppeling tot die minimum te beperk.

c) Ontkoppelkapasitors:Behoorlike plasing van ontkoppelkapasitors is van kritieke belang om voldoende kragoordrag te verseker en kragtoevoergeraas te minimaliseer. Die stapelvolgorde moet nabyheid en nabyheid van die ontkoppelkapasitors aan die krag- en grondvlakke verskaf.

2.2 Termiese bestuur en hitte-afvoer:

Doeltreffende termiese bestuur is van kritieke belang om stroombaanbetroubaarheid en werkverrigting te verseker. Die stapelvolgorde moet die korrekte plasing van krag- en grondvlakke, termiese vias en ander verkoelingsmeganismes in ag neem. Belangrike oorwegings sluit in:

a) Kragvlakverspreiding:Voldoende verspreiding van krag en grondvlakke regdeur die stapel help om hitte weg van sensitiewe komponente te lei en verseker eenvormige temperatuurverspreiding oor die hele bord.

b) Termiese vias:Die stapelvolgorde moet voorsiening maak vir effektiewe termiese via plasing om hitte-afvoer van die binneste laag na die buitenste laag of hitte-afvoer te vergemaklik. Dit help om gelokaliseerde warm kolle te voorkom en verseker doeltreffende hitte-afvoer.

c) Komponentplasing:Stapelvolgorde moet die rangskikking en nabyheid van verwarmingskomponente in ag neem om oorverhitting te voorkom. Behoorlike belyning van komponente met verkoelingsmeganismes soos koelbakke of waaiers moet ook oorweeg word.

2.3 Vervaardigingsbeperkings en kosteoptimalisering:

Die stapelvolgorde moet vervaardigingsbeperkings en kosteoptimalisering in ag neem, aangesien dit 'n belangrike rol speel in die uitvoerbaarheid en bekostigbaarheid van die bord. Oorwegings sluit in:

a) Materiaal beskikbaarheid:Die geselekteerde stapelvolgorde moet ooreenstem met die beskikbaarheid van materiale en hul verenigbaarheid met die geselekteerde PCB-vervaardigingsproses.

b) Aantal lae en kompleksiteit:Die stapelvolgorde moet binne die beperkings van die geselekteerde PCB-vervaardigingsproses ontwerp word, met inagneming van faktore soos aantal lae, boor-aspekverhouding en belyningsakkuraatheid.

c) Koste-optimering:Die stapelvolgorde behoort die gebruik van materiale te optimaliseer en vervaardigingskompleksiteit te verminder sonder om die vereiste werkverrigting en betroubaarheid in te boet. Dit moet daarop gemik wees om koste verbonde aan materiaalafval, proseskompleksiteit en samestelling te verminder.

2.4 Laagbelyning en seinoorspraak:

Die stapelvolgorde moet laagbelyningskwessies aanspreek en seinoorspraak minimaliseer wat seinintegriteit negatief kan beïnvloed. Belangrike oorwegings sluit in:

a) Simmetriese stapeling:Simmetriese stapeling van seinlae tussen krag- en grondlae help om koppeling te minimaliseer en oorspraak te verminder.

b) Differensiële paar roetering:Die stapelvolgorde moet toelaat dat die seinlae behoorlik in lyn gebring word vir doeltreffende roetering van hoëspoed differensiële seine. Dit help om seinintegriteit te handhaaf en oorspraak te verminder.

c) Seinskeiding:Die stapelvolgorde moet die skeiding van sensitiewe analoog en digitale seine oorweeg om oorspraak en steuring te verminder.

2.5 Impedansiebeheer en RF/mikrogolfintegrasie:

Vir RF/mikrogolftoepassings is die stapelvolgorde van kritieke belang om behoorlike impedansiebeheer en integrasie te verkry. Sleuteloorwegings sluit in:

a) Beheerde impedansie:Die stapelvolgorde moet voorsiening maak vir beheerde impedansie-ontwerp, met inagneming van faktore soos spoorwydte, diëlektriese dikte en laagrangskikking. Dit verseker korrekte seinvoortplanting en impedansiepassing vir RF/mikrogolfseine.

b) Seinlaagplasing:RF/mikrogolf seine moet strategies naby die buitenste laag geplaas word om interferensie van ander seine te minimaliseer en beter seinvoortplanting te verskaf.

c) RF-afskerming:Die stapelvolgorde moet behoorlike plasing van grond- en afskermlae insluit om RF/mikrogolfseine teen steuring te isoleer en te beskerm.

3.Tussenlaagverbindingsmetodes

3.1 Deurgate, blinde gate en begrawe gate:

Vias word wyd gebruik in gedrukte stroombaan (PCB) ontwerp as 'n manier om verskillende lae te verbind. Hulle word gate deur al die lae van die PCB geboor en is bedek om elektriese kontinuïteit te verskaf. Deurgate verskaf 'n sterk elektriese verbinding en is relatief maklik om te maak en te herstel. Hulle benodig egter groter boorpuntgroottes, wat waardevolle spasie op die PCB opneem en roete-opsies beperk.

Blinde en begrawe vias is alternatiewe tussenlaagverbindingsmetodes wat voordele bied in ruimtebenutting en roetebuigsaamheid.

Blinde deure word vanaf die PCB-oppervlak geboor en eindig in binnelae sonder om deur alle lae te gaan. Hulle laat verbindings tussen aangrensende lae toe, terwyl dieper lae onaangeraak gelaat word. Dit maak voorsiening vir meer doeltreffende gebruik van bordspasie en verminder die aantal boorgate. Begrawe vias, aan die ander kant, is gate wat heeltemal ingesluit is binne die binneste lae van die PCB en nie na die buitenste lae strek nie. Hulle verskaf verbindings tussen binneste lae sonder om die buitenste lae te beïnvloed. Begrawe vias het groter ruimtebesparende voordele as deurgate en blinde vias omdat dit geen spasie in die buitenste laag opneem nie.

Die keuse van deurgate, blinde vias en begrawe vias hang af van die spesifieke vereistes van die PCB-ontwerp. Deurgate word tipies gebruik in eenvoudiger ontwerpe of waar robuustheid en herstelbaarheid primêre bekommernisse is. In hoëdigtheidontwerpe waar ruimte 'n kritieke faktor is, soos handtoestelle, slimfone en skootrekenaars, word blinde en begrawe vias verkies.

3.2 Mikropore enHDI tegnologie:

Mikrovias is gate met 'n klein deursnee (gewoonlik minder as 150 mikron) wat hoëdigtheid tussenlaagverbindings in PCB's verskaf. Hulle bied aansienlike voordele in miniaturisering, seinintegriteit en roetebuigsaamheid.

Mikrovias kan in twee tipes verdeel word: deur-gat mikrovias en blinde mikrovias. Mikrovia's word gebou deur gate vanaf die boonste oppervlak van die PCB te boor en deur alle lae te strek. Blinde mikrovias, soos die naam aandui, strek net na spesifieke interne lae en dring nie alle lae binne nie.

Hoë-digtheid interconnect (HDI) is 'n tegnologie wat mikrovias en gevorderde vervaardigingstegnieke gebruik om hoër stroombaandigtheid en werkverrigting te bereik. HDI-tegnologie maak voorsiening vir die plasing van kleiner komponente en strenger roetering, wat lei tot kleiner vormfaktore en hoër seinintegriteit. HDI-tegnologie bied verskeie voordele bo tradisionele PCB-tegnologie in terme van miniaturisering, verbeterde seinvoortplanting, verminderde seinvervorming en verbeterde funksionaliteit. Dit laat meerlaagontwerpe met veelvuldige mikrovias toe, waardeur interkonneksielengtes verkort word en parasitiese kapasitansie en induktansie verminder word.

HDI-tegnologie maak ook die gebruik van gevorderde materiale soos hoëfrekwensie-laminate en dun diëlektriese lae moontlik, wat van kritieke belang is vir RF/mikrogolftoepassings. Dit bied beter impedansiebeheer, verminder seinverlies en verseker betroubare hoëspoedseinoordrag.

3.3 Tussenlaagverbindingsmateriaal en -prosesse:

Die keuse van tussenlaagverbindingsmateriaal en -tegnieke is van kritieke belang om goeie elektriese werkverrigting, meganiese betroubaarheid en vervaardigbaarheid van PCB's te verseker. Sommige algemeen gebruikte tussenlaagverbindingsmateriaal en -tegnieke is:

a) Koper:Koper word wyd gebruik in geleidende lae en vias van PCB's as gevolg van sy uitstekende geleidingsvermoë en soldeerbaarheid. Dit word gewoonlik op die gat geplaat om 'n betroubare elektriese verbinding te verskaf.

b) Soldeer:Soldeertegnieke, soos golfsoldeer of hervloeisoldeer, word dikwels gebruik om elektriese verbindings tussen deurgate op PCB's en ander komponente te maak. Wend soldeerpasta aan die via en dien hitte toe om die soldeersel te smelt en 'n betroubare verbinding te vorm.

c) Elektroplatering:Elektroplateringstegnieke soos elektrolose koperplatering of elektrolitiese koper word gebruik om vias te plateer om geleiding te verbeter en goeie elektriese verbindings te verseker.

d) Verbinding:Bindingstegnieke, soos gombinding of termokompressiebinding, word gebruik om gelaagde strukture saam te voeg en betroubare onderlinge verbindings te skep.

e) Diëlektriese materiaal:Die keuse van diëlektriese materiaal vir die PCB-stapeling is krities vir tussenlaagverbindings. Hoëfrekwensie laminate soos FR-4 of Rogers laminate word dikwels gebruik om goeie seinintegriteit te verseker en seinverlies te minimaliseer.

3.4 Deursnitontwerp en betekenis:

Die deursnee-ontwerp van die PCB-stapel bepaal die elektriese en meganiese eienskappe van die verbindings tussen lae. Sleuteloorwegings vir deursnee-ontwerp sluit in:

a) Laagrangskikking:Die rangskikking van sein-, krag- en grondvlakke binne 'n PCB-stapel beïnvloed seinintegriteit, kragintegriteit en elektromagnetiese interferensie (EMI). Behoorlike plasing en belyning van seinlae met krag- en grondvlakke help om geraaskoppeling te minimaliseer en lae induktansie-terugpaaie te verseker.

b) Impedansiebeheer:Dwarssnitontwerp moet beheerde impedansievereistes in ag neem, veral vir hoëspoed digitale of RF/mikrogolf seine. Dit behels toepaslike keuse van diëlektriese materiale en diktes om die verlangde kenmerkende impedansie te bereik.

c) Termiese bestuur:Die deursnee-ontwerp moet effektiewe hitte-afvoer en termiese bestuur in ag neem. Behoorlike plasing van krag- en grondvlakke, termiese vias en komponente met verkoelingsmeganismes (soos hittesinks) help om hitte te verdryf en optimale bedryfstemperature te handhaaf.

d) Meganiese betroubaarheid:Seksie-ontwerp moet meganiese betroubaarheid in ag neem, veral in toepassings wat aan termiese siklusse of meganiese spanning onderwerp kan word. Behoorlike keuse van materiale, bindingstegnieke en stapelopstelling help om die strukturele integriteit en duursaamheid van die PCB te verseker.

4. Ontwerpriglyne vir 16-laag PCB

4.1 Laagtoewysing en verspreiding:

Wanneer 'n 16-laag stroombaanbord ontwerp word, is dit belangrik om die lae noukeurig toe te ken en te versprei om werkverrigting en seinintegriteit te optimaliseer. Hier is 'n paar riglyne vir vlaktoewysing

en verspreiding:

Bepaal die aantal seinlae wat benodig word:

Oorweeg die kompleksiteit van die stroombaanontwerp en die aantal seine wat herlei moet word. Ken genoeg seinlae toe om alle vereiste seine te akkommodeer, verseker voldoende roeteringspasie en vermy oormatigeopeenhoping. Ken grond- en kragvlakke toe:

Ken ten minste twee binnelae toe aan grond- en kragvlakke. 'n Grondvlak help om 'n stabiele verwysing vir seine te verskaf en verminder elektromagnetiese interferensie (EMI). Die kragvlak bied 'n lae-impedansie kragverspreidingsnetwerk wat help om spanningsval te minimaliseer.

Skei sensitiewe seinlae:

Afhangende van die toepassing kan dit nodig wees om sensitiewe of hoëspoed seinlae van lawaaierige of hoëkraglae te skei om interferensie en oorspraak te voorkom. Dit kan gedoen word deur toegewyde grond- of kragvliegtuie tussen hulle te plaas of isolasielae te gebruik.

Verdeel seinlae eweredig:

Versprei seinlae eweredig deur die bordstapel om koppeling tussen aangrensende seine te minimaliseer en seinintegriteit te behou. Vermy die plasing van seinlae langs mekaar in dieselfde stapelarea om tussenlaag-oorspraak te minimaliseer.

Oorweeg hoëfrekwensie seine:

As jou ontwerp hoëfrekwensieseine bevat, oorweeg dit om die hoëfrekwensieseinlae nader aan die buitenste lae te plaas om transmissielyneffekte te minimaliseer en voortplantingsvertragings te verminder.

4.2 Roetering en seinroetering:

Roetering en seinspoorontwerp is van kritieke belang om behoorlike seinintegriteit te verseker en interferensie te minimaliseer. Hier is 'n paar riglyne vir uitleg en seinroetering op 16-laag stroombane:

Gebruik wyer spore vir hoëstroom seine:

Vir seine wat hoë stroom dra, soos krag- en grondverbindings, gebruik wyer spore om weerstand en spanningsval te minimaliseer.

Bypassende impedansie vir hoëspoed seine:

Vir hoëspoedseine, maak seker dat die spoorimpedansie ooreenstem met die kenmerkende impedansie van die transmissielyn om refleksies en seinverswakking te voorkom. Gebruik beheerde impedansie-ontwerptegnieke en korrekte spoorwydteberekeninge.

Minimaliseer spoorlengtes en oorkruispunte:

Hou spoorlengtes so kort as moontlik en verminder die aantal oorkruispunte om parasitiese kapasitansie, induktansie en interferensie te verminder. Optimaliseer komponentplasing en gebruik toegewyde roetelae om lang, komplekse spore te vermy.

Skei hoëspoed- en laespoedseine:

Skei hoëspoed- en laespoedseine om die impak van geraas op hoëspoedseine te verminder. Plaas hoëspoedseine op toegewyde seinlae en hou dit weg van hoëkrag- of raserige komponente.

Gebruik differensiaalpare vir hoëspoed seine:

Om geraas te minimaliseer en seinintegriteit vir hoëspoed differensiële seine te handhaaf, gebruik differensiële paar roeteringstegnieke. Hou die impedansie en lengte van differensiële pare ooreenstem om sein skeef en oorspraak te voorkom.

4.3 Grondlaag en kraglaagverspreiding:

Behoorlike verspreiding van grond- en kragvliegtuie is van kritieke belang om goeie kragintegriteit te bereik en elektromagnetiese interferensie te verminder. Hier is 'n paar riglyne vir grond- en kragvliegtuigopdragte op 16-laag stroombaanborde:

Ken toegewyde grond- en kragvliegtuie toe:

Ken ten minste twee binnelae toe vir toegewyde grond- en kragvlakke. Dit help om grondlusse te minimaliseer, EMI te verminder en 'n lae-impedansie-terugkeerpad vir hoëfrekwensie-seine te verskaf.

Afsonderlike digitale en analoog grondvlakke:

As die ontwerp digitale en analoog afdelings het, word dit aanbeveel om aparte grondvlakke vir elke afdeling te hê. Dit help om geraaskoppeling tussen die digitale en analoog afdelings te verminder en verbeter seinintegriteit.

Plaas grond- en kragvliegtuie naby seinvliegtuie:

Plaas grond- en kragvliegtuie naby die seinvliegtuie wat hulle voer om lusarea te minimaliseer en geraasopvang te verminder.

Gebruik verskeie vias vir kragvliegtuie:

Gebruik veelvuldige vias om kragvliegtuie aan te sluit om krag eweredig te versprei en kragvlakimpedansie te verminder. Dit help om toevoerspanningsval te verminder en verbeter kragintegriteit.

Vermy smal nekke in kragvliegtuie:

Vermy smal nekke in kragvliegtuie aangesien dit stroomophoping kan veroorsaak en weerstand kan verhoog, wat spanningsval en kragvlak ondoeltreffendheid tot gevolg kan hê. Gebruik sterk verbindings tussen verskillende kragvlakareas.

4.4 Termiese pad en via plasing:

Behoorlike plasing van termiese kussings en vias is van kritieke belang om hitte effektief te verdryf en te voorkom dat komponente oorverhit. Hier is 'n paar riglyne vir termiese pad en via plasing op 16-laag stroombaanborde:

Plaas termiese kussing onder hittegenererende komponente:

Identifiseer die hittegenererende komponent (soos 'n kragversterker of hoëkrag-IC) en plaas die termiese pad direk daaronder. Hierdie termiese kussings bied 'n direkte termiese pad om hitte na die interne termiese laag oor te dra.

Gebruik veelvuldige termiese vias vir hitteafvoer:

Gebruik veelvuldige termiese vias om die termiese laag en buitenste laag te verbind om doeltreffende hitte-afvoer te verskaf. Hierdie vias kan in 'n verspringende patroon rondom die termiese pad geplaas word om eweredige hitteverspreiding te verkry.

Oorweeg termiese impedansie en laagstapeling:

By die ontwerp van termiese vias, oorweeg die termiese impedansie van die bordmateriaal en laagstapel. Optimaliseer via grootte en spasiëring om termiese weerstand te minimaliseer en hitte-afvoer te maksimeer.

4.5 Komponentplasing en seinintegriteit:

Behoorlike komponentplasing is van kritieke belang om seinintegriteit te handhaaf en interferensie te minimaliseer. Hier is 'n paar riglyne vir die plasing van komponente op 'n 16-laag stroombaanbord:

Groepverwante komponente:

Groepeer verwante komponente wat deel is van dieselfde substelsel of sterk elektriese interaksies het. Dit verminder spoorlengte en verminder seinverswakking.

Hou hoëspoedkomponente naby:

Plaas hoëspoedkomponente, soos hoëfrekwensie-ossillators of mikrobeheerders, naby mekaar om spoorlengtes te minimaliseer en behoorlike seinintegriteit te verseker.

Minimaliseer die spoorlengte van kritieke seine:

Verminder die spoorlengte van kritieke seine om voortplantingsvertraging en seinverswakking te verminder. Plaas hierdie komponente so na as moontlik.

Afsonderlike sensitiewe komponente:

Skei geraassensitiewe komponente, soos analoogkomponente of laevlaksensors, van hoëkrag- of raserige komponente om interferensie te minimaliseer en seinintegriteit te handhaaf.

Oorweeg om kapasitors te ontkoppel:

Plaas ontkoppelkapasitors so na as moontlik aan die kragpenne van elke komponent om skoon krag te verskaf en spanningskommelings te minimaliseer. Hierdie kapasitors help om die kragtoevoer te stabiliseer en geraaskoppeling te verminder.

5. Simulasie- en analise-instrumente vir opstapelontwerp

5.1 3D modellering en simulasie sagteware:

3D-modellering en simulasiesagteware is 'n belangrike hulpmiddel vir stapelontwerp omdat dit ontwerpers toelaat om virtuele voorstellings van PCB-stapels te skep. Die sagteware kan lae, komponente en hul fisiese interaksies visualiseer. Deur die opeenhoping te simuleer, kan ontwerpers potensiële kwessies soos seinoorspraak, EMI en meganiese beperkings identifiseer. Dit help ook om die rangskikking van komponente te verifieer en die algehele PCB-ontwerp te optimaliseer.

5.2 Seinintegriteit analise gereedskap:

Seinintegriteit analise gereedskap is van kritieke belang vir die ontleding en optimalisering van die elektriese werkverrigting van PCB stapels. Hierdie instrumente gebruik wiskundige algoritmes om seingedrag te simuleer en te ontleed, insluitend impedansiebeheer, seinrefleksies en geraaskoppeling. Deur simulasie en analise uit te voer, kan ontwerpers moontlike seinintegriteitskwessies vroeg in die ontwerpproses identifiseer en die nodige aanpassings maak om betroubare seinoordrag te verseker.

5.3 Termiese analise gereedskap:

Termiese analise-instrumente speel 'n belangrike rol in stapelontwerp deur die termiese bestuur van PCB's te analiseer en te optimaliseer. Hierdie gereedskap simuleer hitteafvoer en temperatuurverspreiding binne elke laag van die stapel. Deur kragafvoer en hitte-oordragpaaie akkuraat te modelleer, kan ontwerpers warm kolle identifiseer, die plasing van koperlae en termiese vias optimaliseer en behoorlike verkoeling van kritieke komponente verseker.

5.4 Ontwerp vir vervaardigbaarheid:

Ontwerp vir vervaardigbaarheid is 'n belangrike aspek van stapelontwerp. Daar is 'n verskeidenheid sagteware-instrumente beskikbaar wat kan help verseker dat die geselekteerde opstapel doeltreffend vervaardig kan word. Hierdie instrumente gee terugvoer oor die haalbaarheid om die verlangde stapeling te bereik, met inagneming van faktore soos materiaalbeskikbaarheid, laagdikte, vervaardigingsproses en vervaardigingskoste. Dit help ontwerpers om ingeligte besluite te neem om stapeling te optimaliseer om vervaardiging te vereenvoudig, die risiko van vertragings te verminder en opbrengste te verhoog.

6. Stap-vir-stap ontwerpproses vir 16-laag PCB's

6.1 Insameling van aanvanklike vereistes:

In hierdie stap, versamel al die nodige vereistes vir 16-laag PCB ontwerp. Verstaan die PCB se funksionaliteit, vereiste elektriese werkverrigting, meganiese beperkings, en enige spesifieke ontwerpriglyne of standaarde wat gevolg moet word.

6.2 Komponenttoewysing en rangskikking:

Ken komponente op die PCB toe volgens vereistes en bepaal hul rangskikking. Oorweeg faktore soos seinintegriteit, termiese oorwegings en meganiese beperkings. Groepeer komponente gebaseer op elektriese eienskappe en plaas dit strategies op die bord om interferensie te minimaliseer en seinvloei te optimaliseer.

6.3 Opstapelontwerp en laagverspreiding:

Bepaal die stapel-op-ontwerp vir die 16-laag PCB. Oorweeg faktore soos diëlektriese konstante, termiese geleidingsvermoë en koste om die toepaslike materiaal te kies. Ken sein-, krag- en grondvlakke toe volgens elektriese vereistes. Plaas grond- en kragvliegtuie simmetries om 'n gebalanseerde stapel te verseker en seinintegriteit te verbeter.

6.4 Seinroetering en roeteoptimalisering:

In hierdie stap word seinspore tussen komponente gelei om behoorlike impedansiebeheer, seinintegriteit te verseker en seinoorspraak te minimaliseer. Optimaliseer roetering om die lengte van kritieke seine te minimaliseer, vermy kruising van sensitiewe spore en handhaaf skeiding tussen hoëspoed- en laespoedseine. Gebruik differensiële pare en beheerde impedansie roeteringstegnieke wanneer nodig.

6.5 Tussenlaagverbindings en via plasing:

Beplan die plasing van verbindingsvia's tussen lae. Bepaal die toepaslike deurgangtipe, soos deurgat of blindegat, gebaseer op laagoorgange en komponentverbindings. Optimaliseer via uitleg om seinrefleksies, impedansiediskontinuïteite te minimaliseer en eweredige verspreiding op die PCB te handhaaf.

6.6 Finale ontwerpverifikasie en simulasie:

Voor vervaardiging word finale ontwerpverifikasie en simulasies uitgevoer. Gebruik simulasie-instrumente om PCB-ontwerpe te ontleed vir seinintegriteit, kragintegriteit, termiese gedrag en vervaardigbaarheid. Verifieer die ontwerp teen aanvanklike vereistes en maak die nodige aanpassings om werkverrigting te optimaliseer en vervaardigbaarheid te verseker.

Werk saam en kommunikeer met ander belanghebbendes soos elektriese ingenieurs, meganiese ingenieurs en vervaardigingspanne regdeur die ontwerpproses om te verseker dat aan alle vereistes voldoen word en potensiële probleme opgelos word. Hersien en herhaal ontwerpe gereeld om terugvoer en verbeterings in te sluit.

7. Bedryfsbeste praktyke en gevallestudies

7.1 Suksesvolle gevalle van 16-laag PCB-ontwerp:

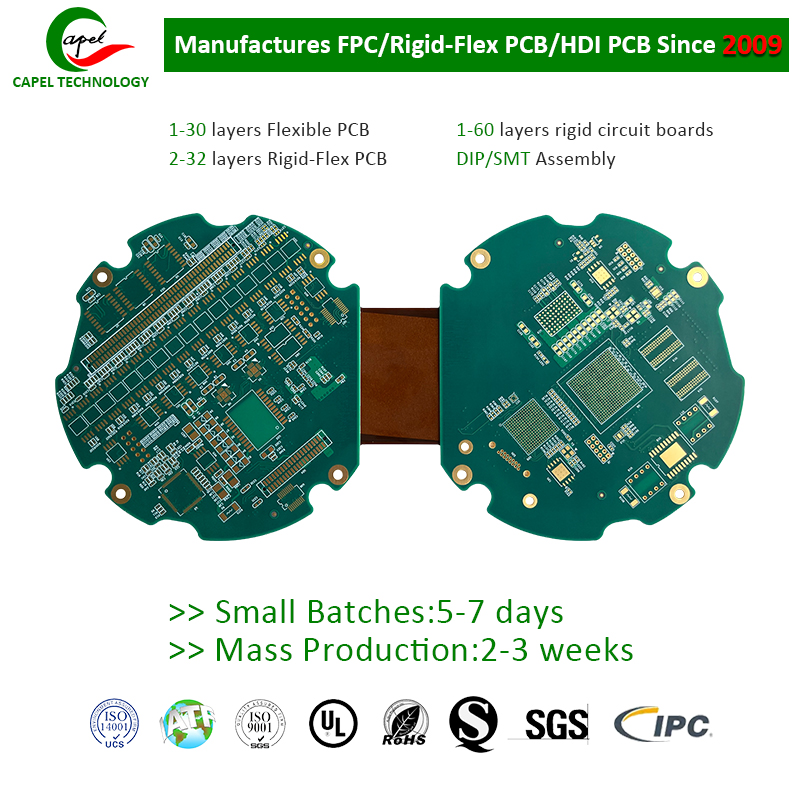

Gevallestudie 1:Shenzhen Capel Technology Co., Ltd. het 'n 16-laag PCB suksesvol ontwerp vir hoëspoed netwerktoerusting. Deur seinintegriteit en kragverspreiding noukeurig in ag te neem, bereik hulle voortreflike werkverrigting en verminder hulle elektromagnetiese interferensie. Die sleutel tot hul sukses is 'n volledig geoptimaliseerde stapelontwerp wat gebruik maak van beheerde impedansie-roeteringstegnologie.

Gevallestudie 2:Shenzhen Capel Technology Co., Ltd. het 'n 16-laag PCB vir 'n komplekse mediese toestel ontwerp. Deur 'n kombinasie van oppervlakmontering en deurgatkomponente te gebruik, het hulle 'n kompakte dog kragtige ontwerp bereik. Versigtige komponentplasing en doeltreffende roetering verseker uitstekende seinintegriteit en betroubaarheid.

7.2 Leer uit mislukkings en vermy slaggate:

Gevallestudie 1:Sommige PCB-vervaardigers het probleme met seinintegriteit ondervind in die 16-laag PCB-ontwerp van kommunikasietoerusting. Die redes vir mislukking was onvoldoende oorweging van impedansiebeheer en 'n gebrek aan behoorlike grondvlakverspreiding. Die les wat geleer is, is om seinintegriteitvereistes noukeurig te ontleed en streng impedansiebeheer-ontwerpriglyne af te dwing.

Gevallestudie 2:Sommige PCB-vervaardigers het vervaardigingsuitdagings in die gesig gestaar met sy 16-laag PCB as gevolg van ontwerpkompleksiteit. Die oorbenutting van blinde deure en dig verpakte komponente lei tot vervaardigings- en monteerprobleme. Die les wat geleer is, is om 'n balans te vind tussen ontwerpkompleksiteit en vervaardigbaarheid gegewe die vermoëns van die gekose PCB-vervaardiger.

Om slaggate en slaggate in 16-laag PCB-ontwerp te vermy, is dit noodsaaklik om:

a. Verstaan die vereistes en beperkings van die ontwerp deeglik.

b.Gestapelde konfigurasies wat seinintegriteit en kragverspreiding optimaliseer. c.Verdeel en rangskik komponente versigtig om werkverrigting te optimaliseer en vervaardiging te vereenvoudig.

d.Verseker behoorlike roeteringstegnieke, soos die beheer van impedansie en die vermyding van oormatige gebruik van blinde vias.

e. Werk saam en kommunikeer effektief met alle belanghebbendes betrokke by die ontwerpproses, insluitend elektriese en meganiese ingenieurs en vervaardigingspanne.

f.Voer omvattende ontwerpverifikasie en simulasie uit om potensiële probleme te identifiseer en reg te stel voor vervaardiging.

Postyd: 26 September 2023

Terug